Information Security and Cryptography

Marc Joye

Michael Tunstall Editors

# Fault Analysis in Cryptography

### Information Security and Cryptography

#### Series Editors

David Basin Ueli Maurer

#### Advisory Board

Martín Abadi Ross Anderson Michael Backes Ronald Cramer Virgil D. Gligor Oded Goldreich Joshua D. Guttman Arjen K. Lenstra John C. Mitchell Tatsuaki Okamoto Kenny Paterson Bart Preneel

For further volumes: http://www.springer.com/series/4752

Marc Joye · Michael Tunstall Editors

# Fault Analysis in Cryptography

Editors

Marc Joye

Technicolor

1 avenue de Belle Fontaine

Cesson-Sévigné Cedex

35576

France

Michael Tunstall Department of Computer Science University of Bristol Woodland Road Bristol BS8 1UB UK

ISSN 1619-7100 ISBN 978-3-642-29655-0 ISBN 978-3-642-29656-7 (eBook) DOI 10.1007/978-3-642-29656-7 Springer Heidelberg New York Dordrecht London

Library of Congress Control Number: 2012939112

ACM Computing Classification: E.3, B.1

#### © Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Foreword**

Fault attacks is an active area of research in cryptography, currently explored in hundreds of research papers and dedicated conferences. This book is the first comprehensive treatment of the subject covering both the theory and practice of these attacks as well as defense techniques.

Fault attacks exploit the fact that computers sometimes make mistakes. These mistakes can result from a programming error, as in the case of the infamous Intel floating-point bug. Or they can result from direct interference by an attacker, say by running the computer in a hostile environment. This book explores what happens to cryptographic algorithms when the computer implementing the algorithm makes a calculation error. Very often these errors, called faults, can have disastrous consequences, rendering the system completely insecure. As an extreme example, a single mistake during the calculation of an RSA digital signature can completely expose the signer's secret key to anyone who obtains the faulty signature. Over the years it has been shown that a wide range of cryptographic algorithms succumb to fault attacks. This book does a beautiful job of presenting powerful fault attacks against a wide range of systems.

Preventing fault attacks without sacrificing performance is nontrivial. Over the years a number of innovative ideas have been proposed for efficiently verifying cryptographic computations. Many defense strategies are described in the book, some of which are already deployed in real-world cryptographic libraries. Nevertheless, many implementations remain vulnerable. I was thrilled to see the material covered in the book and hope that it will make fault defense the standard practice in the minds of developers.

Dan Boneh Stanford University

#### **Preface**

One of the first examples of fault injection in microprocessors was unintentional. May and Woods noticed that radioactive particles produced by elements present in the packaging materials used to protect microprocessors were energetic enough to cause faults [277]. Specifically, it was observed that  $\alpha$  particles were released by uranium-235, uranium-238, and thorium-230 residues present in the packaging, decaying to lead-206. These particles were able to create a large enough charge that bits in sensitive areas of a chip could be made to flip. These elements were only present in two or three parts per million, but this concentration was sufficient to change the behavior of a microprocessor.

Further research into the physical effects that could affect the behavior of microprocessors included studying and simulating the effects of cosmic rays on semiconductors [435]. While the effect of cosmic rays are very weak at ground level because of the Earth's atmosphere, their effect becomes more pronounced in the upper atmosphere and outer space. This is important as faults in airborne electronic systems have potentially catastrophic consequences. This provoked research by organizations such as NASA and Boeing to "harden" electronic devices so that they are able to operate in harsh environments.

Since then other physical means of inducing errors have been discovered but all of these have had somewhat similar effect. In 1992, for example, Habing determined that a laser beam could be used to imitate the effect of charge particles on microprocessors [173]. The different faults that can be produced have been characterized to enable the design of suitable protection mechanisms.

The first academic publication that discussed using such a fault to intentionally break a cryptographic algorithm was described by Boneh, DeMillo, and Lipton in 1997 [56]. It was observed, among other things, that an implementation of RSA that uses the Chinese Remainder Theorem to compute a modular exponentiation is very sensitive to fault attacks (see Sect. 8.2). A similar publication followed this that described a fault to intentionally break a secret key cryptographic algorithm [49]. More specifically, this attack applied techniques from differential cryptanalysis that would allow an attacker to exploit a fault to break an implementation of DES (see Sect. 3.3).

x Preface

Aumüller, Bier, Fischer, Hofreiter, and Seifert published the first academic paper detailing an implementation of one of these attacks [18]. They describe an implementation of the attack by Boneh et al. breaking an implementation of RSA computed using the Chinese Remainder Theorem.

Since then numerous attacks and countermeasures have been proposed and implemented. This book presents a summary of the state of the art in the theoretical and practical aspects of fault analysis and countermeasures. *Happy reading*!

Rennes (France), Bristol (UK), April 2011

Marc Joye Michael Tunstall

#### **Contents**

#### Part I Introductory Material 1 Side-Channel Analysis and Its Relevance to Fault Attacks . . . . . 3 Elisabeth Oswald and François-Xavier Standaert Part II Fault Analysis in Secret Key Cryptography 2 Attacking Block Ciphers..... 19 Christophe Clavier 3 37 Matthieu Rivain 4 Differential Fault Analysis of the Advanced 55 Christophe Giraud 5 73 Jörn-Marc Schmidt and Marcel Medwed 6 On Countermeasures Against Fault Attacks 89 Kaouthar Bousselam, Giorgio Di Natale, Marie-Lise Flottes and Bruno Rouzeyre

xii Contents

| Par                   | t III Fault Analysis in Public Key Cryptography                                                                                                                 |     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7                     | A Survey of Differential Fault Analysis Against Classical RSA Implementations                                                                                   | 111 |

| 8                     | Fault Attacks Against RSA-CRT Implementation                                                                                                                    | 125 |

| 9                     | Fault Attacks on Elliptic Curve Cryptosystems                                                                                                                   | 137 |

| 10                    | On Countermeasures Against Fault Attacks on Elliptic Curve Cryptography Using Fault Detection                                                                   | 157 |

| 11                    | Design of Cryptographic Devices Resilient to Fault Injection Attacks Using Nonlinear Robust Codes Kahraman D. Akdemir, Zhen Wang, Mark Karpovsky and Berk Sunar | 171 |

| 12                    | Lattice-Based Fault Attacks on Signatures                                                                                                                       | 201 |

| 13                    | Fault Attacks on Pairing-Based Cryptography                                                                                                                     | 221 |

| Part IV Miscellaneous |                                                                                                                                                                 |     |

| 14                    | Fault Attacks on Stream Ciphers                                                                                                                                 | 239 |

| 15                    | Interaction Between Fault Attack Countermeasures and the Resistance Against Power Analysis Attacks                                                              | 257 |

Contents xiii

| Part V Implementing Fault Attacks |                                                                                                                                                            |     |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 16                                | Injection Technologies for Fault Attacks on Microprocessors  Alessandro Barenghi, Guido M. Bertoni, Luca Breveglieri, Mauro Pelliccioli and Gerardo Pelosi | 275 |

| 17                                | Global Faults on Cryptographic Circuits                                                                                                                    | 295 |

| 18                                | Fault Injection and Key Retrieval Experiments on an Evaluation Board                                                                                       | 313 |

| Ref                               | erences                                                                                                                                                    | 333 |

#### **Contributors**

Kahraman D. Akdemir Worcester Polytechnic Institute, USA

Abdulaziz Alkhoraidly University of Waterloo, Waterloo, Canada

Alessandro Barenghi Politecnico di Milano, Italy

Alexandre Berzati CEA Leti, France

Guido M. Bertoni STMicroelectronics, Italy

Kaouthar Bousselam Université de Montpellier II, France

Luca Breveglieri Politecnico di Milano, Milan, Italy

Cécile Canovas-Dumas CEA Leti, France

Christophe Clavier XLIM & Université de Limoges, France

Jean-Luc Danger Telecom ParisTech, France

Giorgio Di Natale LIRMM / CNRS, France

Agustín Domínguez-Oviedo Tecnológico de Monterrey, Mexico

Nadia El Mrabet Université de Caen, France

Marie-Lise Flottes LIRMM / CNRS, France

Toshinori Fukunaga NTT Information Sharing Platform Laboratories, Japan

Christophe Giraud Oberthur Technologies, France

Shigeto Gomisawa The University of Electro-Communications, Japan

Louis Goubin Université de Versailles Saint-Quentin-en-Yvelines, France

Sylvain Guilley Telecom ParisTech, France

Arash Hariri The University of Western Ontario, Canada

xvi Contributors

M. Anwar Hasan University of Waterloo, Waterloo, Canada

Paolo Ienne École Polytechnique Fédérale de Lausanne, Switzerland

Mark Karpovsky Boston University, USA

Chong Hee Kim Université Catholique de Louvain, Belgium

Israel Koren University of Massachusetts, USA

Yang Li The University of Electro-Communications, Japan

**Marcel Medwed** Université Catholique de Louvain, Belgium; Graz University of Technology, Austria

Phong Q. Nguyen École Normale Supérieure, France

Kazuo Ohta The University of Electro-Communications, Japan

Elisabeth Oswald University of Bristol, UK

Dan Page University of Bristol, UK

Mauro Pelliccioli Politecnico di Milano, Italy

Gerardo Pelosi Politecnico di Milano, Italy

Jean-Jacques Quisquater Université Catholique de Louvain, Belgium

**Francesco Regazzoni** Université Catholique de Louvain, Belgium; University of Lugano, Switzerland

Arash Reyhani-Masoleh The University of Western Ontario, Canada

Matthieu Rivain CryptoExperts, France

Bruno Rouzeyre Université de Montpellier II, France

**Kazuo Sakiyama** The University of Electro-Communications, Japan

Jörn-Marc Schmidt Graz University of Technology, Austria

François-Xavier Standaert Université Catholique de Louvain, Belgium

Berk Sunar Worcester Polytechnic Institute, USA

**Junko Takahashi** NTT Information Sharing Platform Laboratories, The University of Electro-Communications, Japan

Mehdi Tibouchi École Normale Supérieure, France

Elena Trichina STMicroelectronics, Italy

Frederik Vercauteren Katholieke Universiteit Leuven, Belgium

**Zhen Wang** Boston University, USA

## Part I Introductory Material

# Chapter 1 Side-Channel Analysis and Its Relevance to Fault Attacks

Elisabeth Oswald and François-Xavier Standaert

**Abstract** Side-channel attacks are a class of attacks where an attacker deduces the internal state of a device by observing information that leaks during the normal functioning of the device. In this chapter we describe side-channel analysis and its relevance to fault attacks. Side-channel analysis is typically used to extract information about cryptographic keys. However, we will be concentrating on how it can be used as a means to identify target operations and as a trigger mechanism for fault attacks.

#### 1.1 Introduction

Side-channel attacks are a class of attacks where an attacker will attempt to deduce what is occurring inside a device by observing information that leaks during the normal functioning of the device. The first publication that mentions a side-channel attack is [422]. In 1956, MI5 mounted an operation to decipher communications between Egyptian embassies. The communications were enciphered using Hagelin machines [207]. Enciphering occurred by routing electronic signals from a keyboard through seven rotating wheels to generate a ciphertext. The "key" was the initial setting of these seven wheels. The machine was reset every morning by the clerk

F.-X. Standaert is an associate researcher of the Belgian Fund for Scientific Research (FNRS-F.R.S.).

E. Oswald (⊠)

Department of Computer Science, University of Bristol,

Bristol, UK

e-mail: Elisabeth.Oswald@bristol.ac.uk

F.-X. Standaert Crypto Group, Université Catholique de Louvain, Louvain-la-Neuve, Belgium who would be sending messages. MI5 managed to plant a microphone in close proximity to one of these machines. This allowed the initial settings to be determined by listening to them being made every morning. This would have allowed MI5 to decipher intercepted communications with another Hagelin machine set to the same key. In practice MI5 was only able to determine a certain number of wheel settings because of the difficulty of distinguishing the noise of the wheels being set from background noise. This made deciphering more complex, but not impossible, as the number of possible keys was significantly reduced by the partial information.

In this chapter we describe side-channel analysis and its relevance to fault attacks. Side-channel analysis is typically used to try to reveal information on cryptographic keys. However, we will be concentrating on identifying target operations and on how to trigger a mechanism to inject a fault.

The first academic publication of a side-channel attack described an attack based on observing the time required to compute a given operation [239]. However, the overall time required to compute an operation is not relevant to the discussion of side-channel analysis with regard to fault attacks.

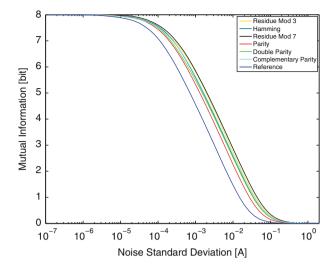

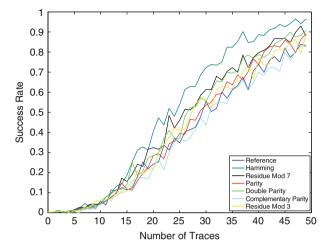

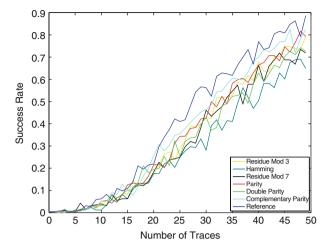

Subsequent publications involved analyzing acquisitions of the instantaneous power consumption [240] or electromagnetic emanations [153, 331]. In each case there are two types of attack, which we will discuss in more detail in this chapter.

- The analysis of one acquisition to determine information on the operations being computed; we elaborate on this in Sect. 1.3.

- The statistical analysis of multiple traces to reveal information, described in Sect. 1.4.

#### 1.2 Background

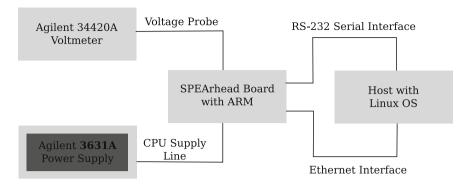

In this section we describe the equipment that one would require to take acquisitions that could be used to conduct side-channel analysis. We focus on the aforementioned analysis of the power consumption and the electromagnetic field around a microprocessor.

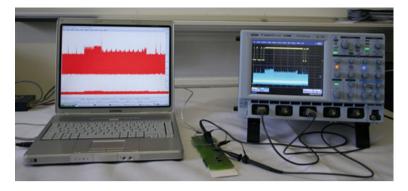

In Fig. 1.1 we show an example of the equipment required to acquire power consumption traces while executing an arbitrary command. A smart card was inserted into an extension card that was then inserted into a standard smart card. An oscilloscope was used to acquire a power consumption trace, visible as a red trace on the laptop computer and as a cyan trace trace on the oscilloscope. This trace represents the voltage drop across a resistor in series with the ground pin of the smart card, typically acquired with a differential probe. A yellow trace is also visible on the oscilloscope that shows the I/O pin of the smart card that is used to trigger the oscilloscope.

It was observed in [153, 331] that the same information is present in the change in the electromagnetic field surrounding a microprocessor. Traces showing the change in the electromagnetic field can be acquired by using a suitable probe. This typically

Fig. 1.1 An example of the equipment one could use to take acquisitions of the instantaneous power consumption of a smart card

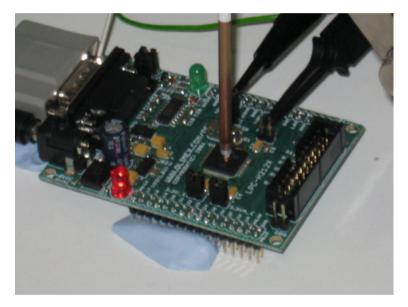

Fig. 1.2 An example of a probe used for acquiring traces of the electromagnetic emanations above an ARM7 microprocessor

consists of a tube formed from a single wire that is then placed perpendicular to the surface of a microprocessor, an example of which is shown in Fig. 1.2.

In this chapter we discuss side-channel analysis using the power consumption as a running example. The same analysis can be made using acquisitions from an electromagnetic probe. However, these acquisitions are typically more noisy and are therefore less suitable for presenting clear examples.

#### 1.3 Simple Power Analysis

Having introduced the basics of commonly exploited leakages and sketched how to capture and record these leakages, we now explain how to use them in simple power analysis (SPA) scenarios to aid fault attacks. The basic idea underlying all these attacks is to identify operations using a side-channel, and to then inject faults into the identified functions. We first explain this idea in more detail by briefly reviewing some examples of what is possible using SPA. We then discuss how someone wishing to implement a fault attack could use these techniques in practice. An attacker may be required to identify an appropriate trigger point for a fault injection mechanism, i.e. to automatically examine a power trace to trigger a fault inducing mechanism.

#### 1.3.1 Case Study: RSA Private Operation

The principal operation of the RSA [349] signature scheme is a modular exponentiation in  $(\mathbb{Z}/N\mathbb{Z})^*$ . That is, a signature s is generated from a message m by computing  $s = \mu(m)^d \mod N$ , where d is the private key, N is the product of two large primes, and  $\mu$  is an appropriate padding function. This signature can be verified by checking whether  $\mu(m)$  is equal to  $s^e \mod n$ . We define  $d \equiv e^{-1} \pmod{\phi(N)}$  where  $\phi$  is Euler's totient function.

One of the most widely known algorithms for implementing an exponentiation is the square-and-multiply algorithm, where an exponent e is read from left to right bit by bit. Starting with an accumulator set to 1, a squaring operation is performed if a bit is equal to 0, and a squaring operation followed by a multiplication (with the value being raised to e) is performed if a bit is equal to 1. This algorithm is detailed in Algorithm 1.1.

```

Algorithm 1.1: Binary left-to-right exponentiation

```

```

Input: m, x < m, d \ge 1, \ell the binary length of d (i.e. 2^{\ell-1} \le d < 2^{\ell})

Output: A = x^d \mod m

1 A \leftarrow x; R \leftarrow x

2 for i = \ell' - 2 Down to 0 do

3 A \leftarrow A^2

4 if (\text{bit}(n, i) \ne 0) then A \leftarrow A \cdot R

5 end

6 return A

```

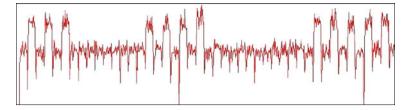

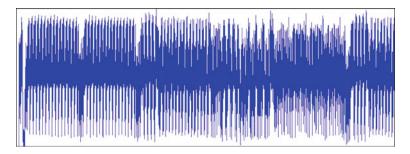

In Fig. 1.3 we show a power consumption trace captured while a microprocessor was computing a modular exponentiation using Algorithm 1.1. A series of operations can be seen in the power consumption that are separated by downward peaks. From the ratio of operations, dictated by Algorithm 1.1, we can determine that the

Fig. 1.3 The power consumption of a microprocessor while computing a modular exponentiation

lower power consumption corresponds to a squaring operation and the higher power consumption corresponds to a multiplication. If we denote a squaring operation as S and a multiplication as M, then the series of operations in Fig. 1.3 is

These directly correspond to the first 41 bits of the exponent used to generate the power consumption trace in Fig. 1.3, which, from the sequence of operations, can be identified as

1111000000001111100000000000011111.

#### 1.3.2 Case Study: AES Encryption

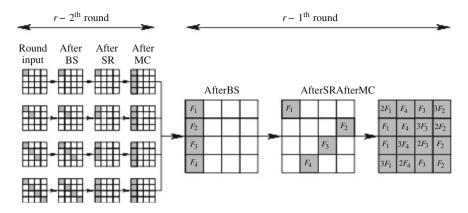

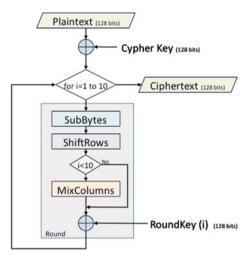

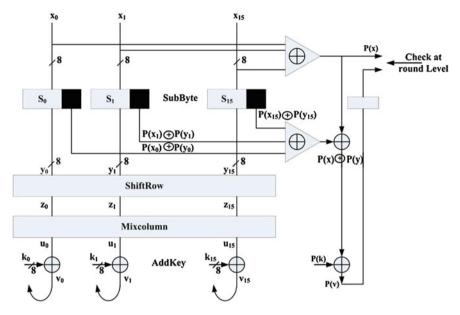

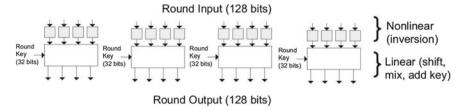

Implementations of block ciphers in small embedded devices are another example of where SPA can be straightforwardly applied in order to identify individual operations or trigger a fault insertion apparatus. Differential fault analysis attacks typically target a specific round of a block cipher. Hence, solutions that allow determining the exact time at which these operations are computed will be useful in this context. In this section we use the Advanced Encryption Standard (AES) as an example. In this section multiplications are considered to be polynomial multiplications over  $\mathbb{F}_{2^8}$  modulo the irreducible polynomial  $x^8 + x^4 + x^3 + x + 1$ . It should be clear from the context when a mathematical expression contains integer multiplication.

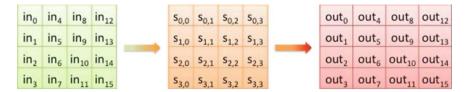

The structure of the Advanced Encryption Standard (AES) [142], as used to perform encryption, is illustrated in Algorithm 1.2. Note that we restrict ourselves to considering AES-128 and that the description omits a permutation typically used to convert the plaintext  $P = (p_0, p_1, \ldots, p_{15})_{(256)}$  and key  $K = (k_0, k_1, \ldots, k_{15})_{(256)}$  into a 4 × 4 array of bytes, known as the state matrix. For example, the 128-bit plaintext input block P and 128-bit ciphertext C are arranged as

$$\begin{pmatrix} p_0 & p_4 & p_8 & p_{12} \\ p_1 & p_5 & p_9 & p_{13} \\ p_2 & p_6 & p_{10} & p_{14} \\ p_3 & p_7 & p_{11} & p_{15} \end{pmatrix} \quad \text{and} \quad \begin{pmatrix} c_0 & c_4 & c_8 & c_{12} \\ c_1 & c_5 & c_9 & c_{13} \\ c_2 & c_6 & c_{10} & c_{14} \\ c_3 & c_7 & c_{11} & c_{15} \end{pmatrix}.$$

#### Algorithm 1.2: The AES-128 encryption function

```

Input: The 128-bit plaintext block P and key K

Output: The 128-bit ciphertext block C

1 X \leftarrow \operatorname{AddRoundKey}(P, K)

2 for i \leftarrow 1 to 10 do

3 | X \leftarrow \operatorname{SubBytes}(X)

4 | X \leftarrow \operatorname{ShiftRows}(X)

5 | if i \neq 10 then

6 | X \leftarrow \operatorname{MixColumns}(X)

7 | end

8 | K \leftarrow \operatorname{KeySchedule}(K)

9 | X \leftarrow \operatorname{AddRoundKey}(X, K)

10 end

11 C \leftarrow X

```

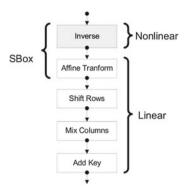

The encryption itself is conducted by the repeated use of a number of round functions:

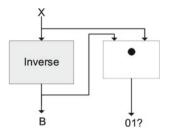

- The SubBytes function is the only nonlinear step of the block cipher. It is a bricklayer permutation consisting of an S-box applied to the bytes of the state. Each byte of the state matrix is replaced by its multiplicative inverse, followed by an affine mapping. Thus the input byte x is related to the output y of the S-Box by the relation,  $y = Ax^{-1} + B$ , where A and B are constant matrices. In the remainder of this paper we will refer to the function S as the SubBytes function and to  $S^{-1}$  as the inverse of the SubBytes function.

- The ShiftRows function is a byte-wise permutation of the state.

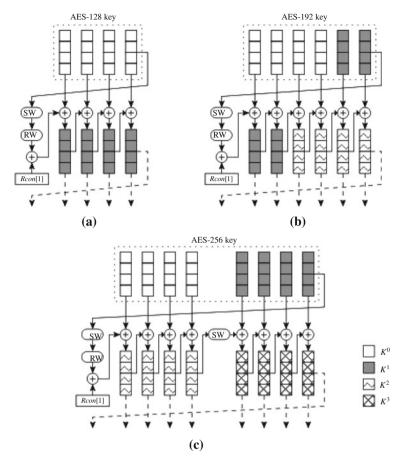

- The KeySchedule function generates the next round key from the previous one. The first round key is the input key with no changes; subsequent round keys are generated using the SubBytes function and XOR operations. Algorithm 1.3 shows how the rth round key is computed from the (r-1)th round key. The value  $h_r$  is a constant defined for the rth round, and  $\ll$  is used to denote a bit-wise left shift.

- The MixColumns function is a bricklayer permutation operating on the state column by column. Each column of the state matrix is considered as a vector where each element belongs to  $\mathbb{F}(2^8)$ . A 4 × 4 matrix

Fig. 1.4 Power consumption trace of a single AES encryption performed by a smart card

$$M = \begin{pmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{pmatrix}$$

whose elements are also in  $\mathbb{F}(2^8)$  (here expressed as a decimal digit) is used to map this column into a new vector.

• AddRoundKey: Each byte of the array is XORed with a byte from a corresponding array of round subkeys.

```

Algorithm 1.3: The AES-128 KeySchedule function

```

```

Input: (r-1)^{th} round key (X = x_i \text{ for } i \in \{1, ..., 16\}).

Output: r^{th} round key X.

1 for i \leftarrow 0 to 3 do

2 | x_{(i \ll 2)+1} \leftarrow x_{(i \ll 2)+1} \oplus S(x_{(((i+1) \land 3) \ll 2)+4})

3 end

4 x_1 \leftarrow x_1 \oplus h_r

5 for i \leftarrow 1 to 16 do

6 | if (i-1) mod 4 \neq 0 then

7 | x_i \leftarrow x_i \oplus x_{i-1}

8 | end

9 end

10 return X

```

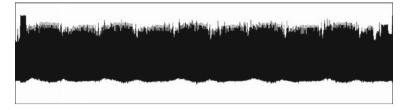

Figure 1.4 shows a power consumption trace taken while a device was performing an AES encryption. It shows a pattern that is repeated ten times, corresponding to the ten AES rounds as described in Algorithm 1.2. The last pattern is slightly different because the MixColumns function is not computed in the last round.

More information can be observed if the power consumption of one round is analyzed in more detail. Figure 1.5 shows the power consumption of an ARM7 microprocessor while it is computing the first round of the AES. Two patterns of 16 peaks can be seen on the left-hand side that correspond to the plaintext and secret key being permuted to enable efficient computation given the matrix representation

**Fig. 1.5** Power consumption trace of a single round of an AES encryption performed by an ARM7 microprocessor

in the specification of the algorithm. This is followed by a pattern of four peaks that correspond to the XOR with the first key byte (the ARM7 has a 32-bit architecture). Following this there is a pattern of 16 peaks that correspond to the SubBytes function. This is followed by two patterns of four peaks that corresponds to the generation of the next subkey. The ShiftRow function occurs between these functions but is not visible in the power consumption. The XOR with this subkey can be seen on the right-hand side of Fig. 1.5, which means that the remaining area between this XOR and the generation of the subkey is where the MixColumns function is computed. However, no obvious pattern can be seen without plotting this portion of the trace with a higher granularity.

In general, such a visual inspection of the leakage traces can be used as a preliminary step before a more powerful attack (such as DPA or DFA), and allows an attacker to determine the parts of the traces that are relevant in a straightforward manner.

The drawback of SPA is its limited granularity, as demonstrated by our example above. It is typically straightforward to identify the AES rounds, as in Fig. 1.4, but identifying to round operations (i.e. AddRoundKey, SubBytes, MixColumns, and ShiftRows) may be more difficult. For example, in Fig. 1.5 the MixColumns is identified by a process of elimination rather than by observing a pattern in the power consumption. Furthermore, devices with larger data buses and ASIC (or FPGA) implementations that process 128 bits in parallel may also make visual inspection more difficult.

#### 1.3.3 Case Study: File Access

As demonstrated in the previous sections, an attacker can potentially recover meaningful information by analyzing a single acquisition of a side-channel. This can be further extended to include branches in the commands being executed by a device. One example of this is the ten rounds of the AES that are visible in Fig. 1.4. If this

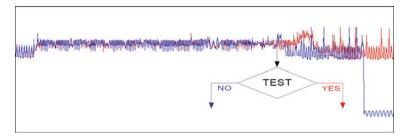

**Fig. 1.6** The power consumption of a microprocessor while evaluating the file access rights on a GSM SIM. The red trace corresponds to a successful file access and the blue trace corresponds to an unsuccessful file access

is implemented as a loop there will be a test at the end of each round to determine if ten rounds have been computed. Another example would be file access rights. Some devices, such as GSM SIMs, consist of a file structure with associated file access conditions. In Fig. 1.6 the power consumption of a SIM that allows access to an arbitrary file is plotted in red, and the power consumption of the same SIM that denies access to an arbitrary file is plotted in blue. Superposing the traces, as in Fig. 1.6, would allow an attacker to determine the moment that file access is granted or denied by the microprocessor.

#### 1.4 Differential Power Analysis

Differential power analysis (DPA) is a natural extension of SPA, in which the adversary conducts intensive data acquisition (e.g. thousands of traces) in order to recover a cryptographic key. This process usually starts by selecting the subkeys *s* that are to be recovered by the attack. In the context of block ciphers (our running example), these subkeys typically correspond to small parts (e.g. bytes) of the master key. Then, the attack can be described as a combination of the following three steps [269]:

- 1. For different plaintexts  $x_i$  and subkey candidates  $s^*$ , the adversary predicts some intermediate values in the target implementation. For example, one could predict S-box outputs  $z_i$  and get values  $v_i^{s^*} = S(x_i \oplus s^*)$ .

- 2. For each of these predicted values, the adversary models the side-channel leakage. For example, if the target block cipher is executed on a CMOS-based microprocessor, the model is typically the Hamming weight (HW) of the predicted values. One then obtains the modelled leakage  $m_i^{s^*} = HW(v_i^{s^*})$ .

- 3. For each subkey candidate  $s^*$ , the adversary finally compares the modelled leakages with the acquisitions produced with the same plaintexts  $x_i$  and a subkey, using a statistical distinguisher of his choice. One commonly chosen distinguisher is Pearson's correlation coefficient [72], i.e. an attacker computes the correlation between the modelled leakage and each point in the acquired traces.

In first-order DPA attacks against unprotected devices, each  $m_i^{s^*}$  is compared with a single point in the traces. Hence, the comparison step is independent of all other points in the acquired trace. In practical attacks, this comparison is applied to many points in the leakage traces and the subkey candidate that performs best is selected by the adversary.

Note also that many distinguishers can be used to detect data dependencies in the leakages. Classical solutions include Kocher's difference of means test [240], Pearson's correlation coefficient [72] and template attacks [82].

#### 1.4.1 Profiled Fault Triggering with DPA

If the effectiveness of SPA in triggering a fault insertion against certain classes of devices becomes limited, it is alternatively possible to exploit DPA for this purpose. However, it is important to note that using DPA implies a modification of the attack scenario. That is, while SPA-based triggering techniques could be used "on the fly", DPA usually makes sense as a preparation stage, to be applied before the application of a fault attack. In fact, most successful DPA attacks come both with the identification of the points of interest in a trace, and with secret key information.

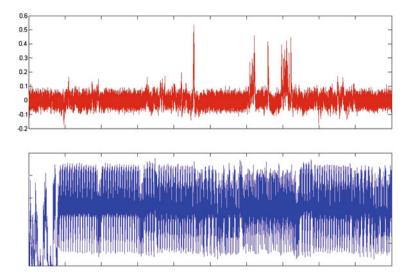

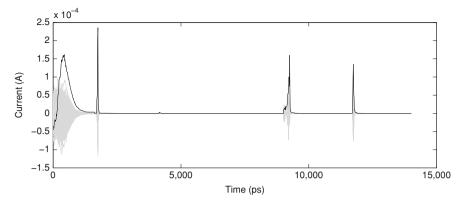

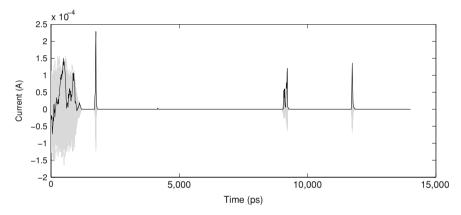

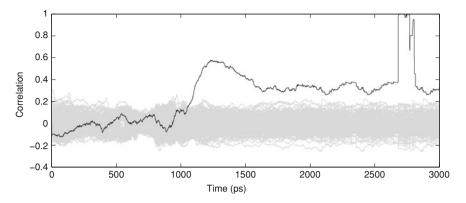

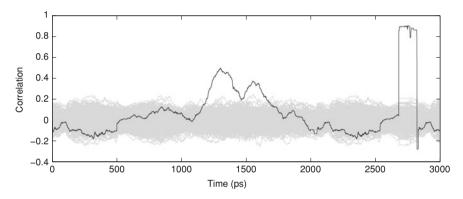

An example is shown in Fig. 1.7, where the lower trace is a single power consumption trace taken during the computation of an AES on an ARM7 microprocessor (as previously considered in Sect. 1.3). The upper trace shows the correlation between the Hamming weight of the output of one byte of the SubBytes function and a series of power consumption traces. The peaks in the correlation trace show at which points in the power consumption trace the predicted byte is manipulated by the microprocessor. This complements the information one can observe using SPA. The first peak corresponds to where the first byte is produced in the SubBytes function and indicates which of the 16 peaks corresponds to that byte being produced. The subsequent peaks in the correlation trace indicate the points in time where the same byte is manipulated in the MixColumns function.

Note that if the key is unknown, only the intermediate values after the first (and before the last) round(s) can initially be predicted by the adversary, i.e. before the diffusion in the cipher makes them dependent on too many key bits. But once a single successful DPA has been applied (i.e. once a master key is known), it is possible to predict any intermediate value in the cipher and consequently to detect its precise execution time for a subsequent fault attack.

#### 1.5 Advanced Scenarios

The previous sections discuss case studies in which power analysis can be used to complement fault injection, essentially for enhancing the triggering aspects. However, most embedded devices for security applications are now protected with various

**Fig. 1.7** An example of Differential Power Analysis applied to AES. The lower trace is an example power consumption trace, and the upper trace is the correlation between the Hamming weight of the output of one byte of the SubBytes function and a series of power consumption traces

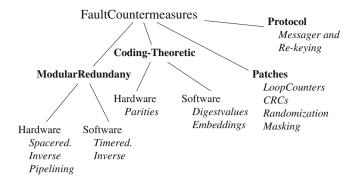

countermeasures against physical attacks. The precise description of these countermeasures and the advanced attacks that can be applied to circumvent them is out of the scope of this chapter. But for completeness, we list certain types of countermeasures, with pointers to further readings.

Regular Algorithms. The information available to an attacker analyzing one trace needs to be limited to the identification of operations, without revealing any information on cryptographic keys. The simplest countermeasure is to use regular algorithms that will compute the same sequence of operations for all possible key values. When computing an RSA signature an alternative is to ensure that the same function is used to compute both operations [85]. This was proposed to allow the continued use of Algorithm 1.1, which is preferable on devices with limited resources. The rest of the countermeasures described in this section apply to DPA.

Data Randomization. The most investigated countermeasure to side-channel analysis is masking (see, e.g. [168, 347]). The intuitive idea behind masking is to split the sensitive data into a number of shares and to perform the encryption operation on the different shares separately. As a consequence, any successful DPA will have to combine the information from several shares (and, if not computed in parallel, time samples) in order to observe key dependencies in the leakages. Attacks on implementations using masking are referred to as 'higher-order' attacks, and Chari et al. showed in [81] that the number of traces required to recover a key from the leakages of a masked implementation increases exponentially in the number of shares, given that a sufficient amount of noise is limiting the quality of the measurements [385]. Masking does not directly impact fault attacks, besides the fact

that it increases the difficulty of finding the time samples corresponding to certain operations with DPA. A fault inserted on a byte of either the masked data or the mask will propagate through the cipher as a fault inserted into the unprotected data [60]. Clearly, under specific fault models, e.g. inducing faults which set mask bytes to 0, masking becomes ineffective. Another idea which uses faults to counter masking is described in Sect. 2.2.6.

Random Ordered Processing. A countermeasure that complements data randomization is to process operations, as much as possible, in a random order. The operations required compute a block cipher will. bv necessity. computed in a deterministic order. However, the individual commands required to compute these operations can be computed in an arbitrary order. If, for example, we consider the SubBytes function, there are 16! possible orders in which the 16 bytes can be treated. The side-channel information is then spread over 16 different points in the trace, which reduces the amount of information available to an attacker. The most common application of this countermeasure is to block ciphers; it has also been shown to be applicable to group exponentiation, often used in public key cryptographic algorithms [401]. This does not prevent an attacker from targeting a particular operation, but will prevent a specific command within that operation with any degree of certainty.

Random Delays. Another countermeasure that affects the location of information in acquired side-channel traces is the use of functions that pause for a random amount of time before continuing. These functions can be inserted between operations to reduce the amount of information available to an attacker. When conducting a side-channel attack, this means that an attacker will have to synchronize the acquisitions before applying a DPA attack. When attempting to inject a fault at a given point in an algorithm, this becomes more of a problem, as the location of a target operation will be distributed around a given point. An attacker will typically seek to inject a fault at a given point and repeat the attack until the fault is injected in the desired operation. Some proposals have been made to try a maximize the size of this distribution [105, 402]. However, given that this countermeasure slows rather than prevents an attacker, it is debatable whether any complex operations are required.

Technology Scaling. We note finally that, for any type of physical attack, technology scaling is likely to have a significant impact [192]. While they cannot be considered as countermeasures in themselves, the resulting modifications of the semiconductor physics (e.g. the increasing importance of static leakages, or variability issues) imply modifications of the typical leakage models and the types of faults that can be assumed for the target devices.

Data Redundancy. Adding redundancy to the data in order to detect faults during the computation of a cryptographic operation is an appealing solution to preventing fault attacks. As detailed in the later chapters of this book, such redundancies can be effective solutions to preventing various types of errors, with high detection rates. But as data randomization only helps to prevent side-channel attacks, data redundancies only help to prevent fault attacks. In fact, if the type of redundancy present in an implementation is public, it can even be used by the adversary, in order to enhance DPA attacks (to reject certain guesses for the intermediate values).

#### 1.6 Conclusion

In this chapter we have given several practical examples of how different types of side-channels can be used to enable fault attacks. In our examples, side-channel attacks are used to determine trigger points for inducing faults. This can be done using simple side-channel attacks, which are typically combined with on-the-fly fault insertion techniques. As an alternative, one can apply differential side-channel attacks to determine (the order of) operations and launch fault attacks with this information. Lastly, we have sketched some advanced scenarios, all of which are related to different types of countermeasures. We have described how each countermeasure may help or hinder fault attacks.

# Part II Fault Analysis in Secret Key Cryptography

# **Chapter 2 Attacking Block Ciphers**

**Christophe Clavier**

Abstract Differential Fault Analysis (DFA) was one of the earliest techniques invented to attack block ciphers by provoking a computational error. In the basic DFA scenario the adversary obtains a pair of ciphertexts both of which encrypt the same plaintext. One of these ciphertexts is the correct result while the other is an erroneous one resulting from a faulty computation. Though applications of DFA to DES and AES have proven to be quite effective, other techniques have also been invented which can threaten block ciphers in different ways. This chapter presents some of these fault analysis methods, including Collision Fault Analysis (CFA) and its close variant Ineffective Fault Analysis (IFA). These methods depart from DFA by the fault model they rely on, by their ability to defeat classical countermeasures against DFA or DPA, or by their application to specific implementations.

#### 2.1 Introduction

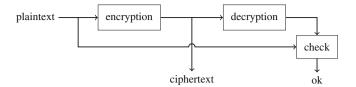

Differential Fault Analysis (DFA) was one of the earliest techniques invented to attack block ciphers by provoking a computational error. In the basic DFA scenario the adversary obtains a pair of ciphertexts that are the result of encrypting the same plaintext. One of these ciphertexts is the correct value while the other is an erroneous one resulting from a faulty computation. Since the two encryptions performed identically up to the point where the fault occurred, the two ciphertexts can be regarded as the outputs of a reduced-round iterated block cipher where the inputs are unknown but show a small (and possibly known) differential. By analyzing the propagation of this differential over a small number of rounds, the adversary seeks to obtain information about the key material involved in the last round.

C. Clavier (⋈)

XLIM (UMR 6172), Université de Limoges, Limoges, France e-mail: christophe.clavier@3il.fr

C. Clavier

Though applications of DFA to DES [49] and AES [127, 160] as described in Sects. 3.3 and 4.2 have proven to be quite effective, other techniques have also been invented which can threaten block ciphers in different ways. This chapter presents some of these fault analysis methods, which depart from DFA by the fault model they rely on, by their ability to defeat classical countermeasures against DFA or DPA, or by their applicability to specific implementations.

An important class of such attack methods is referred to as Collision Fault Analysis (CFA) and has a close variant referred to as Ineffective Fault Analysis (IFA). The first section of this chapter is devoted to the presentation of these two techniques and their successive usages ranging from a first trivial CFA/IFA on unprotected implementations of AES-like algorithms to more elaborate attacks which can either attack implementations protected against both DFA and High-Order DPA, or even reveal the key of a so-called externally encoded DES whose precise specification is unknown to an attacker. Other fault attacks on block ciphers are presented in the second section, including some that explicitly aim to reduce the number of rounds, and others which exploit a perturbation of the initial randomization of substitution tables in DPA-resistant implementations.

## **2.2** Attacks on Block Ciphers by Exploitation of Identical Outputs

#### 2.2.1 Three Resemblant but Different Fault Analysis Methods

#### 2.2.1.1 Collision Fault Analysis

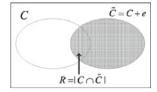

While DFA exploits a differential between a genuine and a faulty ciphertext where the fault occurred in one of the last few rounds of an encryption function E, CFA gains information from a collision event where the two ciphertexts C and  $C^{\frac{f}{2}}$  respectively obtained from a normal and a faulty encryption are equal. An attacker typically first obtains the faulty encryption  $C^{\frac{f}{2}} = E^{\frac{f}{2}}(M_0)$  of an arbitrary plaintext  $M_0$ , and then searches for some particular M which gives the same ciphertext  $E(M) = C = C^{\frac{f}{2}}$  without any fault. Intuitively, it may appear difficult to produce a collision between two outputs of a cryptographic function designed to closely behave as a random function. This difficulty is circumvented by producing the fault very early in the encryption process in order to avoid the avalanche effect between the encryptions of M and  $M_0$ , and by relying on a specific fault model.

One usually adopts a fault model where the fault has a predictable effect on a small portion—a bit or a word—of the intermediate result. Such a classical fault model assumes that a fault occurring during a logical or an arithmetic operation, e.g. an XOR between two bytes, produces a result equal to some constant value

(typically considered to be zero), whatever the input values. When produced at the very beginning of the algorithm a fault will typically corrupt an intermediate value that only depends on one bit or one byte of the input. As the remainder of the intermediate value is not modified, the attacker just has to change that precise bit or byte until a collision with the corrupted value occurs. All other intermediate data being uncorrupted, this local collision propagates to the ciphertexts.

#### 2.2.1.2 Ineffective Fault Analysis

As described above, a CFA attack consists of searching for a plaintext whose corresponding ciphertext collides with some corrupted ciphertext. IFA is slightly different, and applies where an attacker tries to find an input M with the property that when a fault is induced on some precise operation during the encryption process, the intermediate data targeted by the fault is not corrupted, resulting in an identical ciphertext. This kind of analysis gains information from faults which do not locally modify the intermediate result, so-called ineffective faults from which the analysis name is derived.

While usually relying on the same kind of fault model, CFA and IFA differ in many respects. While CFA recovers some piece of information about the key with only one fault, IFA needs to compare pairs of ciphertexts  $(C=E(M),C^{\frac{f}{2}}=E^{\frac{f}{2}}(M))$  until  $C=C^{\frac{f}{2}}$ , so many faults<sup>2</sup> are required before an ineffective one is obtained. On the other hand, the higher complexity of IFA in terms of the number of required fault injections is compensated for by the property that the operation targeted by IFA does not need to occur near the beginning of the algorithm. Since the attacker compares pairs of executions with the same input, any operation during the encryption process can be targeted to identify an ineffective fault. In light of the fact that a fault appears to be ineffective if and only if the natural<sup>3</sup> result of the targeted operation is zero, under the previously described fault model, it is clear that IFA can be considered as a kind of probing tool. Indeed, for any given plaintext it is possible to decide whether the result of any arbitrary targeted operation<sup>4</sup> is zero or not.

Another property specific to IFA is that an attacker does not actually require the value of any faulty ciphertext. The only information that is required is whether the fault had an effect or not. As a consequence, IFA is not thwarted by the classical countermeasure against DFA, which consists in checking the computation and withholding the output if a fault is detected. Indeed, whether a fault is detected or not

<sup>&</sup>lt;sup>1</sup> An exception to this usually adopted fault model for CFA is given by the collision/differential fault attack from Hemme in the first rounds of DES, described in Sects. 2.2.3 and 3.5. This attack is applicable even if the fault produces a random modification of an S-box output.

<sup>&</sup>lt;sup>2</sup> For instance, under a byte-oriented fault model, 128 (or 256) faults are required on average per ineffective fault event when the input of the targeted operation is chosen (or not chosen).

<sup>&</sup>lt;sup>3</sup> I.e. without fault.

<sup>&</sup>lt;sup>4</sup> Provided that this operation is susceptible to the considered faults.

C. Clavier

provides an attacker with the same information as whether or not the fault corrupted the ciphertext.

Finally, note that IFA relies on the fact that the attacker can safely decide that a fault attempt has been ineffective because of the natural value of the targeted data rather than because the fault did not occur. When performing IFA, it is thus very important that the fault injection tool be considered highly reliable.

#### 2.2.1.3 Safe-Error Analysis

A third fault analysis method which exploits the identity of outputs of cryptographic algorithms is the analysis of so-called safe-errors, which we refer to as safe-error Analysis (SEA). This method was first introduced to break a private exponentiation of the RSA cryptosystem [204, 427, 429]. The basic principle consists of modifying some internal data and inferring the value of a private exponent bit from whether this modification resulted in an identical or a different output. Two examples of such analysis on a binary square and multiply exponentiation are: (i) the perturbation of a multiplication in an *always multiply* version of the left-to-right binary exponentiation algorithm, and (ii) including a dummy register in a right-to-left version of the algorithm. In both cases, depending on the particular value of the current exponent bit, the modified data may or may not be used in the sequel of the computation. The latter case corresponds to a safe-error which results in no modification of the algorithm output.

At first, ineffective fault analysis and safe-error analysis look quite similar. Indeed, they both infer information about a secret from whether an induced fault affected the output or not. Actually, there is a conceptual difference between IFA and SEA. In safe-error analysis the data that is targeted by the fault is actually modified, and the output is not modified simply because the modified data is not used. In contrast, an ineffective fault targets data involved in the computation of the algorithm, but because of the fault model and the data value, this data is not modified. In summary, IFA probes a data value while SEA probes a data usage.

A consequence of the difference between these two techniques is that IFA is highly dependent on the effect a fault has on the data being processed while SEA is not. A safe-error will be safe whatever the resulting value of the targeted data, so SEA is applicable in the general random error model. In contrast, ineffective fault analysis usually requires a more restrictive *stuck-at* fault model.

In the remainder of this section, we describe a series of research papers which consider CFA and IFA techniques to recover secret keys of block ciphers. We present them in the chronological order, which roughly corresponds to a trend of increasing ability to defeat countermeasures.

#### 2.2.2 Bit-Wise Collision/Ineffective Fault Analysis on AES

The first attack from the CFA/IFA family was proposed by Blömer et al. [55], where they apply this technique to the AES algorithm. They assume a fault model where an attacker is able to force to 0 any chosen individual bit of an intermediate result. While they advocate its practicality, this fault model can be considered, according to the authors, as a rather strong one.

The principle of their attack is quite simple. An attacker first encrypts an all-zeros plaintext and obtains the corresponding reference ciphertext. Then for each arbitrary bit of the output of the first AddRoundKey operation, a faulty execution is performed where the fault sets this particular bit to 0. If the resulting ciphertext and the reference one are the same then the corresponding key bit is 0. If they differ the corresponding key bit is 1. By scanning all the bits of the first AddRoundKey output, the whole AES key is recovered with 128 fault injections.

Due to the bit-oriented nature of the fault model, this attack can be considered either as a degenerate form of CFA<sup>5</sup> or as an IFA. The computation checking countermeasure does not prevent the attack since only whether or not the fault corrupted the reference ciphertext is informative, not the value of the eventually corrupted result.

Interestingly, one can notice that this attack applies not only to the AES cipher, but more generally to the whole class of block ciphers whose very first operation, and the only one involving the plaintext, is an XOR with the key. Note also that the attack does not require the knowledge of the transformation subsequent to the first XOR with the key. It is thus applicable to any (even unknown) algorithm belonging to this class.

#### 2.2.3 Collision Fault Analysis on DES

Designing a collision fault analysis on a Feistel network presents a specific difficulty. This is because, when encrypting a modified version of the initial plaintext  $M_0$  used for the faulty execution, the input differential is involved in both the left and the right paths of the function. It is thus impossible to provoke a modification *only* on the input of one targeted operation and obtain a collision of intermediate results at the very beginning of the function.

Hemme dealt with this difficulty [178] by using the concept of characteristic, borrowed from differential cryptanalysis [46].<sup>6</sup> A characteristic is a set of prescribed differentials that an execution may follow from one round to another. Hemme considers only characteristics whose differential after k = 2, 3 or 4 rounds is the same

<sup>&</sup>lt;sup>5</sup> The probability that the faulty ciphertext is not corrupted is as much as  $\frac{1}{2}$ .

<sup>&</sup>lt;sup>6</sup> Hemme's attack can be regarded as a CFA since the adversary eventually finds a plaintext which encrypts to the same ciphertext as the faulty one. On the other hand it can also be considered as a kind of DFA since the adversary must analyze which differential characteristic could lead to the colliding message. The reader will find a more detailed description of this attack in Sect. 3.5.

24 C. Clavier

as the differential that may have been produced by a fault. Assuming an attacker can modify the output  $Y_k$  of the kth round to  $Y_k \oplus \varepsilon$  where  $\varepsilon$  belongs to a prescribed set defined by the fault model, a pool of characteristics is created which includes, for each possible  $\varepsilon$ , the most probable characteristic ending after k rounds with a null differential on the left side and a differential equal to  $\varepsilon$  on the right side. After obtaining a faulty ciphertext, and for each  $\varepsilon$ , the attacker tries to exhibit a normal execution which follows the k-round  $(0, \varepsilon)$ -characteristic belonging to the pool. Provided that  $\varepsilon$  is the actual differential effect of the fault, a normal execution following the  $(0, \varepsilon)$ -characteristic on k rounds starts the (k + 1)th round with the same intermediate data as the faulty one, and results in a colliding ciphertext. Each obtained collision gives some information about the first round key  $K_1$ . This information is gathered by counting how many times each key candidate is suggested by a colliding pair. An improved version of the attack which makes use of an extended pool of characteristics can retrieve the whole  $K_1$  with about 400,  $1 \times 10^4$  and  $5 \times 10^6$  faulty executions when k is respectively equal to 2, 3 and 4.

One benefit of this attack is the possibility to attack the DES by fault analysis even when the implementation is protected against classical DFA by recomputing the last few rounds of a block cipher with a verification of the result. Note that this is an advantage only when the attacker does not have access to a decryption function that uses the same key. In the case where the attacker can both encrypt and decrypt any data of his choice, the redundancy of the last few rounds only is not sufficient to prevent DFA. Indeed, an attacker could then decrypt any input C while inducing a fault at the beginning of the algorithm (preferably during the second round) and obtain the faulty output M'. Then he can encrypt M' without fault and get C'. With respect to M', C' is a genuine ciphertext, while C is a faulty one analogous to what would have resulted from a classical DFA on the penultimate round.

## 2.2.4 Defeating a DPA-Resistant AES by Collision Fault Analysis

Amiel et al. presented several fault attacks which apply to DPA-resistant implementations of AES and DES [12]. In this section, we describe two of these that are collision fault analyses applied to AES.

<sup>&</sup>lt;sup>7</sup> The author chose the set of 32 one-bit errors at the end of the round function. While this choice is naturally suited for a bit-oriented fault model, the author noticed that it also happens to be the best one for the less restrictive byte-oriented random error fault model.

<sup>&</sup>lt;sup>8</sup> The attack also necessitates  $4 \times 10^4$ ,  $1.11 \times 10^6$  and  $8.10 \times 10^8$  normal executions respectively.

#### 2.2.4.1 Attacking the First AddRoundKey

A simple CFA attack on AES consists of an adaptation of the attack described in Sect. 2.2.2 to a byte-oriented fault model. Given the faulty ciphertext  $C^{\frac{1}{2}}$  produced by encrypting  $M_0$ , and producing a fault which forces to zero the output of the ith XOR operation in the first AddRoundKey, the attacker exhaustively encrypts all 256 plaintexts  $M=(m_0,\ldots,m_{15})$  which coincide with  $M_0$ , except for the byte  $m_i$ , until one of the ciphertexts collides with  $C^{\frac{1}{2}}$ . The plaintext byte  $m_i$  leading to a collision verifies that  $m_i \oplus k_i = 0$ , so the attacker decides that  $k_i$  is equal to this particular  $m_i$ . By scanning all 16 XOR operations, this attack allows a key to be completely recovered with only 16 faulty executions.

While quite efficient, this attack does not apply when the implementation is protected against first-order DPA by a Boolean masking scheme. In such implementations, all intermediate bytes are masked by an XOR with a random value R which is different from one execution to another, but which is the same from one byte to another. During the first AddRoundKey, each byte  $m_i$  of the plaintext is thus XORed with a masked key byte  $\tilde{k}_i = k_i \oplus R$ . When one tries to apply the above CFA on the result of the ith iteration of the AddRoundKey, the physical zero value forced on the XOR output actually corresponds to a logical value equal to R. While exhausting all  $m_i$ , the collision occurs when the logical XOR output is also equal to the random mask R of the faulty execution. This occurs for  $m_i$  such that  $m_i \oplus k_i = R$ , so the attacker erroneously decides that the key byte is equal to  $k_i \oplus R$  instead of  $k_i$ . As the value R is unknown to the attacker, and different from one faulty execution to another, the attack fails.

Amiel et al. [12] devised a variant of the CFA that can break such DPA-resistant implementations of AES. The method is based on the observation from [21, 300] that a fault may allow an attacker to prematurely terminate a **for** loop before it has gone through all its iterations. If the memory location where the result of the XOR between the plaintext and the key is stored has not been used previously, then there are good odds that it is in an uninitialized state and contains bits all set to 0.9 Now, suppose that one produces a fault two iterations before the end of the loop of the AddRoundKey. Then all 14 first result bytes are correct, but the last two are both have a physical value equal to zero, meaning a logical value equal to some random mask R that is identical for these two bytes. Encrypting all  $2^{16}$  plaintexts where  $m_{14}$  and  $m_{15}$  take all possibilities will produce a collision for  $(m_{14}, m_{15})$ , verifying that

$$m_{14} \oplus k_{14} = R$$

and  $m_{15} \oplus k_{15} = R$ .

An attacker will not know R but can nevertheless infer that

$$k_{14} \oplus k_{15} = m_{14} \oplus m_{15}$$

.

The size of the key space is thus reduced from  $2^{128}$  to  $2^{120}$ .

<sup>&</sup>lt;sup>9</sup> Or all set to 1 depending on the logical representation of the physical state.

C. Clavier

By repeating the attack with the three last result bytes unaffected by the loop, the colliding ciphertext is obtained when logical values  $m_{13} \oplus k_{13}$ ,  $m_{14} \oplus k_{14}$ , and  $m_{15} \oplus k_{15}$  are all equal to a same unknown value  $R^{10}$

$$m_{13} \oplus k_{13} = R$$

,  $m_{14} \oplus k_{14} = R$  and  $m_{15} \oplus k_{15} = R$ .

Combining the first two equations now also reveals the value of  $k_{13} \oplus k_{14}$ .

Note that the exhaustive search on  $(m_{13}, m_{14}, m_{15})$  does not cost  $2^{24}$  encryptions but only  $2^{16}$  since one can restrict the search to tuples of the form  $(m_{13}, m_{14}, m_{14} \oplus \delta_{14,15})$  where  $\delta_{14,15} = k_{14} \oplus k_{15}$  is known.

The attack continues repeatedly in the same way, each time revealing the value of  $k_i \oplus k_{i+1}$  for  $i=12,11,\ldots,0$ , ending with the knowledge of the complete key up to an XOR with a constant of the form  $(c,c,\ldots,c)$ . The correct value is identified by exhaustively trying the 256 remaining candidates. Overall the attack necessitates 15 faulty encryptions and  $15 \times 2^{16} \approx 2^{20}$  normal encryptions.

A common complementary countermeasure against DPA consists in computing as much as possible in a random order. Note that the above attack can also be adapted to the case where the first AddRoundKey loop is executed in a random order. One needs to precompute a dictionary of approximately  $2^{23}$  ciphertexts, which may be somewhat time consuming. A trade-off can speed up this precomputation by generating only a fraction of the dictionary at the cost of an increased number of faulty executions. An interesting practical property of the attack on the random order implementation is that the attacker does not need to change the instant of the perturbation from one fault injection to another.

Both attacks have been practically performed on smart cards. These experiments are described in detail in [400].

#### 2.2.4.2 Attacking the Key Transfer from NVM to RAM

Prior to its use in the computation of a block cipher, each key byte must be XORed with the same random mask value R that is used to randomize any substitution table. This key masking with the value  $(R, R, \ldots, R)$  commonly occurs when the key is transferred from nonvolatile memory (NVM) to RAM. For security purposes the key stored in NVM is also typically masked, where the mask is full size, meaning that every mask byte will be different, but static and diversified from one device to another. Denoting this full-size long-term mask by  $r = (r_0, r_1, \ldots, r_{15})$ , the masked key in NVM is equal to

$$\tilde{K}_{NVM} = (k_0 \oplus r_0, \dots, k_{15} \oplus r_{15})$$

while the masked key in RAM is equal to

$<sup>^{10}</sup>$  Note that the value of R does not necessarily remain the same from one faulty ciphertext to another.

# Algorithm 2.1: Key masking

```

Input: \tilde{K}_{NVM} = (k_0 \oplus r_0, \dots, k_{15} \oplus r_{15})

r = (r_0, r_1, \dots, r_{15}), R

Output: \tilde{K}_{RAM} = (k_0 \oplus R, \dots, k_{15} \oplus R)

1 for i \leftarrow 0 to 15 do

2 \mid \tilde{K}_{RAM,i} \leftarrow \tilde{K}_{NVM,i} \oplus R \ \tilde{K}_{RAM,i} \leftarrow \tilde{K}_{RAM,i} \oplus r_i

3 end

4 return \tilde{K}_{RAM}

```

$$\tilde{K}_{RAM} = (k_0 \oplus R, \dots, k_{15} \oplus R)$$

.

The mask conversion performed during the transfer follows Algorithm 2.1 with the difference that key bytes are actually processed in a random order. By faulting the loop so that only the first iteration has executed, the uninitialized memory space storing  $\tilde{K}_{RAM}$  physically contains 15 bytes equal to zero and another one at a random index i equal to  $k_i \oplus R$ . This corresponds to a logical value of the form  $(R, \ldots, R, k_i, R, \ldots, R)$ , which is the actual key used in the faulty encryption of  $M_0$ .

The attack consists in precomputing a dictionary of about  $2^{20}$  ciphertexts produced by the encryption of the reference plaintext  $M_0$  under all keys of the previous form where i,  $k_i$  and R take all possible values. A search of the faulty ciphertext in the dictionary immediately reveals  $k_i$ . Each new faulty execution gives the opportunity to learn the value of a key byte at a different index. An average of only 54 faults allows all 16 key bytes to be determined. Note that the dictionary does not depend on the actual value of the attacked key.

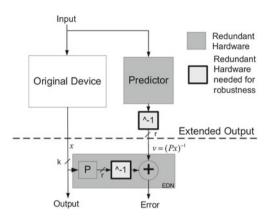

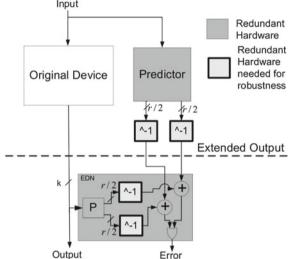

# 2.2.5 Ineffective Fault Analysis on Externally Encoded DES

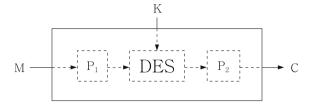

Contrarily to Kerckhoffs' principle, many applications of modern cryptography still adopt the *security by obscurity* paradigm. A particular way of designing a proprietary algorithm consists in surrounding a well-known and widely used block cipher E with two secret external encoding permutations  $P_1$  and  $P_2$  (one-to-one mappings over the input and output spaces respectively), leading to the new, secret, obfuscated block cipher  $E' = P_2 \circ E \circ P_1$ . By basing the construction on a well-known block cipher E we allow the design to inherit proven or empirical cryptographic strength. Also, the two secret encodings  $P_1$  and  $P_2$  ensure that inputs to and outputs from E cannot be known by an attacker, so physical attacks requiring this knowledge should not be feasible.

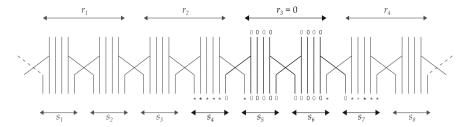

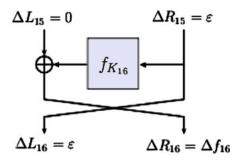

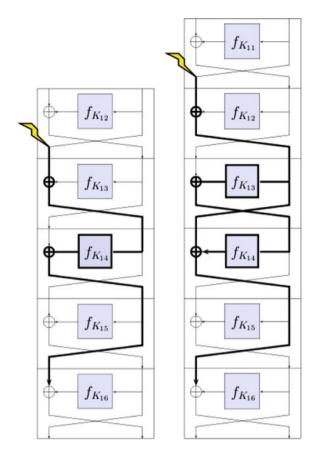

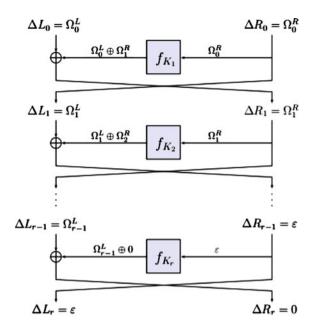

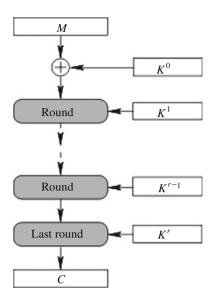

A particular case studied by Clavier [93] depicted in Fig. 2.1 considers E instantiated as the DES function. Despite the impossibility of applying classical DFA [49],

28 C. Clavier

**Fig. 2.1** A DES obfuscated by secret layers  $P_1$  and  $P_2$

which needs the output of the block cipher, and CFA [178], described in Sect. 2.2.3, which needs the control of the DES input, the author devised an ineffective fault analysis which recovers the secret key and applies to any member of the large class of unknown (to the attacker) cryptographic functions.

The attack assumes a classical software implementation of DES on an eight-bit architecture. Also, we assume an attacker is able to precisely control which instruction is executed when a fault is injected. As for other CFAs/IFAs the fault model assumes that a fault injected during the execution of an XOR between two eight-bit operands results in a zero 11 output whatever the input operand values were. Finally, the attacker is supposed to have control over the input given to the encryption function E' as well as knowledge of its output. 12

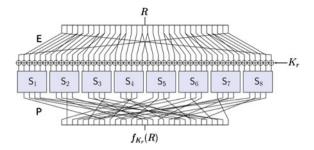

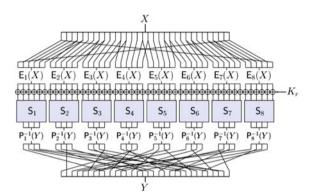

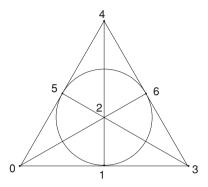

The attack is somewhat complex and makes use of *pairs* of related ineffective faults. We now give a sketch of the principle of a basic version of the attack. As we assume an eight-bit architecture, there are 12 XOR operations per round: eight for the computation of the inputs of each S-box—denoted by  $xor\_key[j](j=1,\ldots,8)$ —and four others at the end of the round for combining its 32-bit output with the left part—denoted by  $xor\_left[i]$  ( $i=1,\ldots,4$ ). The attack intensively uses IFA to probe the output of these different eight-bit XOR operations that may appear at any round.

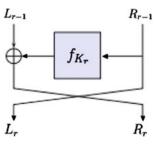

First, suppose that for some arbitrary plaintext M, a fault injected during some  $xor\_left[i]$  at round (h-1) turns out to be ineffective (i.e. the ciphertext obtained with M by faulting this XOR is identical to the one obtained with the same input without fault). This implies that the corresponding output byte is zero. Thus, eight of the 32 bits at the input of the next round h are known to be 0. The subsequent permutation expands them to 12 bits, which are involved in four adjacent S-Boxes at round h as in Fig. 2.2. Now, suppose that for another execution with the same plaintext M, a fault on  $xor\_key[j]$  (for  $j \in \{2i-1, 2i\}$ ) at round h also turns out to be ineffective. Then we know that the input h of this S-box is one of the four preimages of h of h as h is the XOR between a key byte h and a six-bit value having five

<sup>&</sup>lt;sup>11</sup> Note that the attack works equally well if the faulted XOR output is supposed to be any arbitrary known constant instead of zero.

<sup>&</sup>lt;sup>12</sup> These assumptions may be relaxed, since an attacker only needs to be able to replay many different arbitrary inputs, and to detect whether two outputs are equal.

$<sup>^{13}</sup>$  As the S-box is a compressive function from six-bit inputs to four-bit outputs, any preimage of  $S_j(0)$  behaves exactly as the input 0—which has been forced in the faulty execution—and thus produces the same ciphertext.

Fig. 2.2 A zero byte through the expansive permutation

bits known to be 0, we clearly see that  $k_j$  belongs to a set of only eight possible values, which reveals three bits of information about the key.

Overall, the attack repeatedly tries to detect a plaintext producing such a rare pair of related ineffective faults. As much information as possible is gathered by exploiting this kind of event on every possible loci—defined by a couple (xor\_left[i], xor\_key[j])—at every round. According to simulation results, the median residual entropy on the key is reduced from 56 to 26.49 bits (or 22.32 bits) after using  $5 \times 10^4$  faults (or  $1 \times 10^6$  faults). The author also described an improved version of this attack which gains information from more complex kinds of events. This improved attack achieves a median residual entropy of 13.95 bits (or 6.68 bits) after using  $5 \times 10^4$  faults (or resp.  $1 \times 10^5$  faults).

Compared to fault analysis on known cryptosystems, this attack requires a large number of fault injections. This can be considered as a fair price to pay for the 'magic' property of being able to retrieve the key of such unknown functions regardless of the two secret external encodings  $P_1$  and  $P_2$ .

#### 2.2.6 Passive and Active Combined Attacks on AES

The Boolean masking countermeasure that the two CFA attacks described above in Sect. 2.2.4 can bypass is only intended to protect against first-order DPA. State-of-the-art implementations must actually protect against high-order analyses, as introduced by Messerges [284]. The basic principle of such a countermeasure is to use a Boolean masking scheme based on one random byte that is different from one execution to another (as is the case for a first-order countermeasure), also from one S-box operation to another and from one round to another.

The recent attack presented by Clavier et al. in [94] actually succeeds in breaking even this kind of protection. The state-of-the-art implementation considered by the authors implements the S-box description from Oswald et al. [313] and is designed to resist HO-DPA attacks such as those presented in [11, 270]. The method used to break this implementation is a passive and active combined attack. The passive part of the attack consists in an adaptation of Correlation Power Analysis (CPA), originally described by Brier et al. [72]. As with the original analysis on unprotected

30 C. Clavier

implementations, an attacker predicts, under some guess about a key byte, the series—one value for each power curve—of intermediate data manipulated during the AES computation. The difference with this classical scheme is that the targeted intermediate data is not the output of a first round S-box, but rather the random value by which this S-box is masked. Provided the value of this random mask can be predicted, under a key guess, for each execution, a CPA can be performed which will show a correlation peak for the correct guess at each instant the mask is manipulated. The need to identify, up to the corresponding key byte, the series of values taken by some random mask is precisely the reason why the passive part of the attack is preceded by an active phase which identifies the random series by means of a collision fault analysis.

As often, the target of this CFA is an output byte of the first AddRoundKey which is forced to zero by a fault. In the present implementation the plaintext M and the key K have been respectively masked, before they are XORed together, by two 16-byte randoms rm and rk respectively. Iteration i of the AddRoundKey thus computes  $(m_i \oplus rm_i) \oplus (k_i \oplus rk_i) = (m_i \oplus k_i) \oplus r_i$  with  $r_i = rm_i \oplus rk_i$  being the random value used to mask the ith S-box in the first round. As forcing to zero this XOR output is equivalent to introducing a differential equal to  $\delta = m_i \oplus k_i \oplus r_i$ , the attacker is able to identify  $k_i \oplus r_i$ , which is precisely the value for the ith plaintext byte that produces a collision with the faulty ciphertext. Thus, for each faulty execution, the attacker identifies the value  $k_i \oplus r_i$  by means of a CFA, and stores the corresponding power curve. When sufficiently many  $k_i \oplus r_i$  values and corresponding curves have been obtained, it is possible to perform a CPA where the series of  $r_i$  is predicted by simply guessing  $k_i$ . On average, 126 faults are enough to collect traces with 100 different  $r_i$  values, while 1,568 are required to perform the CPA with all 256 occurrences. Note that this attack is applicable even if the 16 XOR operations are computed in a random order. In that case the attacker has to search for the colliding ciphertext in an extended set of  $2^{12}$  plaintexts where the input byte to modify can be in any position. The plaintext producing the collision automatically informs the attacker about the index i of the XOR corrupted by the fault. The attack strategy is slightly different since the different sets of power curves for all possible indices must be collected at the same time rather than successively.

The attack described above does not apply in the case where the computation verification countermeasure is implemented since no corrupted ciphertext is then given to the attacker. In that case it is still possible to adapt the attack by preferring an IFA strategy. When the plaintext byte  $m_i$  is set to the value u, each injected fault is an attempt to obtain a power curve for which  $k_i \oplus r_i = u$ . The probability of success of each attempt is  $2^{-8}$  (or  $2^{-12}$  in the case of random order), so the expected number of faults required to collect n power curves with different masks for each attacked key byte amounts to  $2^{12} \times n$  (or  $2^{16} \times n$ ). This is certainly a large number of faults, so this attack is hardly practical, but a door is opened here to break strongly protected implementations which include at the same time: high-order Boolean masking, computation verification and random order execution.

Note that an interesting and unexpected property of the ineffective fault variant is that it is easier to perform when a computation verification countermeasure is

implemented than when one is not. Indeed, when such a countermeasure is present the attack becomes a known plaintext attack instead of a chosen plaintext attack.

# 2.3 Other Fault Attacks on Block Ciphers

# 2.3.1 Reducing the Number of Rounds

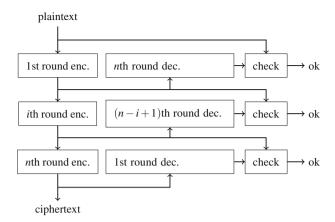

Most block ciphers are *iterated cryptosystems*, which are families of cryptographically strong functions that iterate *n* times a weaker round function. As the security of the block cipher is an increasing function of the number of rounds, an obvious attack path could be to try to produce a perturbation in the normal sequencing which would reduce the number of rounds. This idea has originally been formulated in [15], where the authors suggest corrupting the appropriate loop variable or conditional jump by means of a glitch in either the clock or the power supply to the chip. In the following we give the descriptions of two concrete experiments which put this idea into practice.

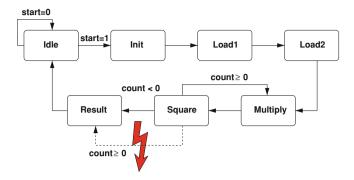

### 2.3.1.1 Round Reduction Using Faults on AES

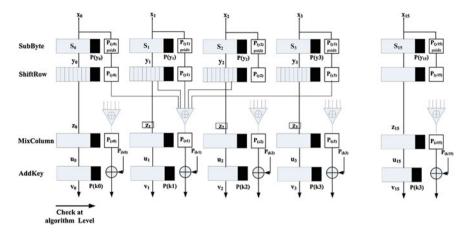

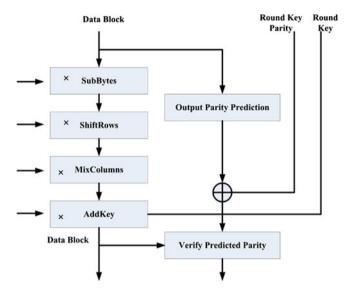

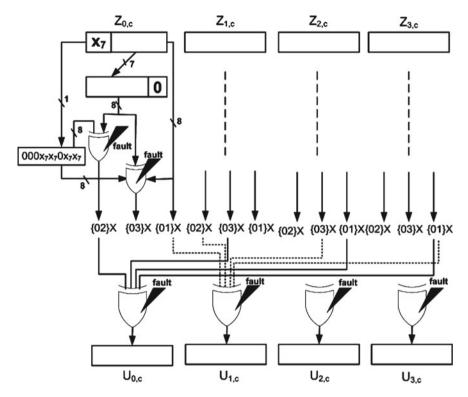

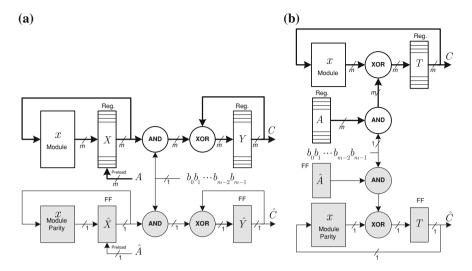

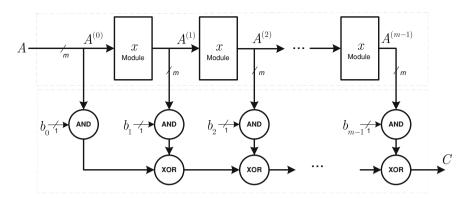

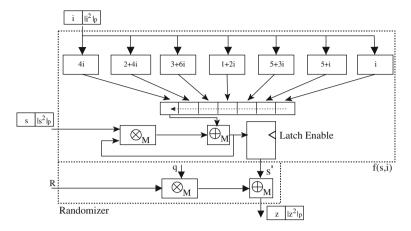

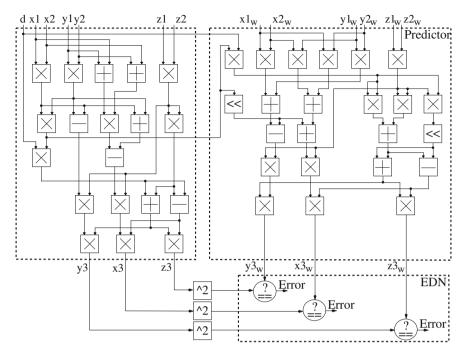

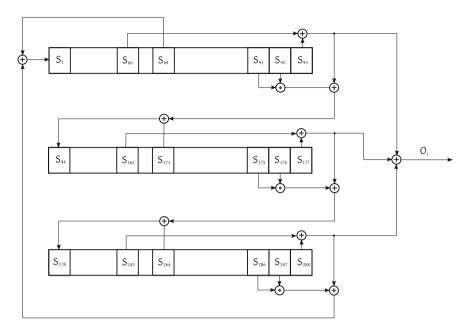

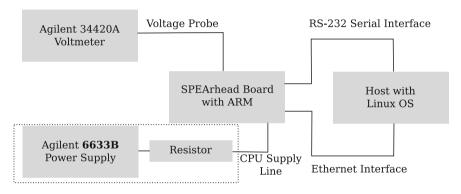

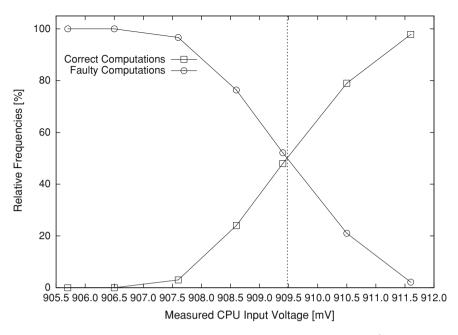

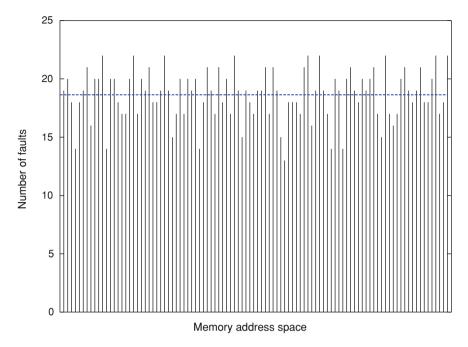

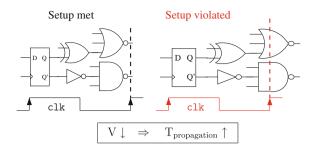

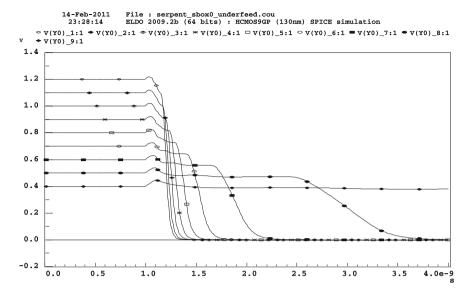

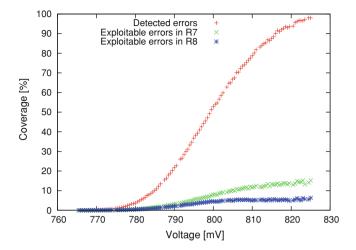

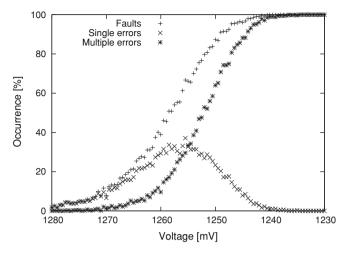

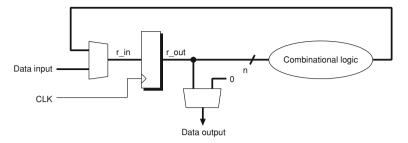

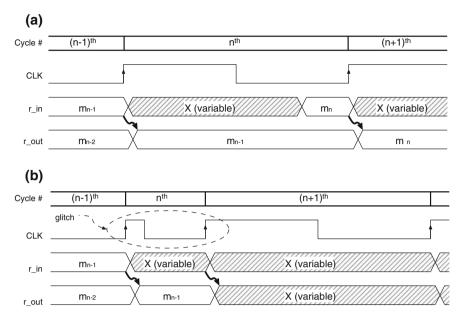

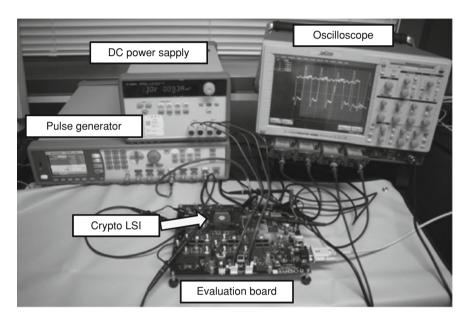

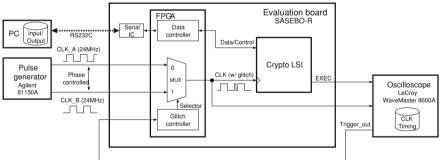

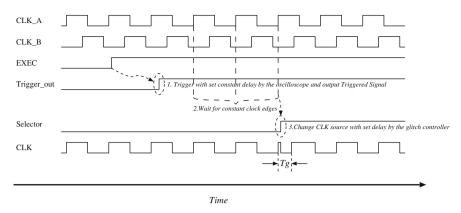

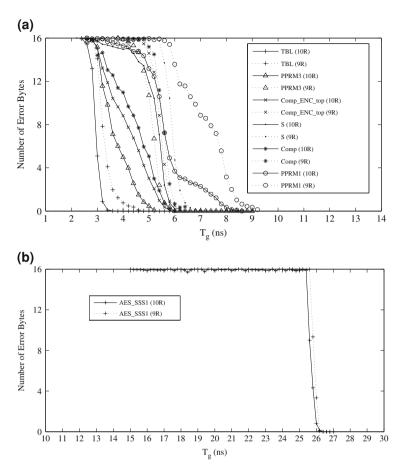

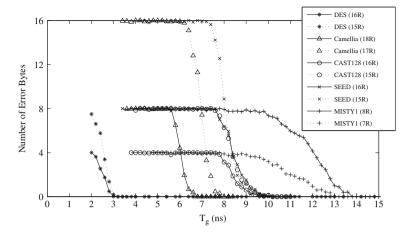

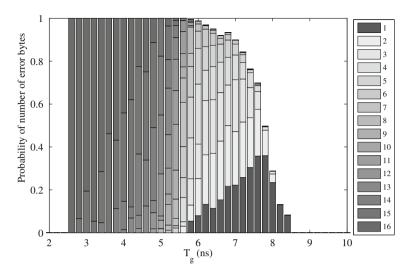

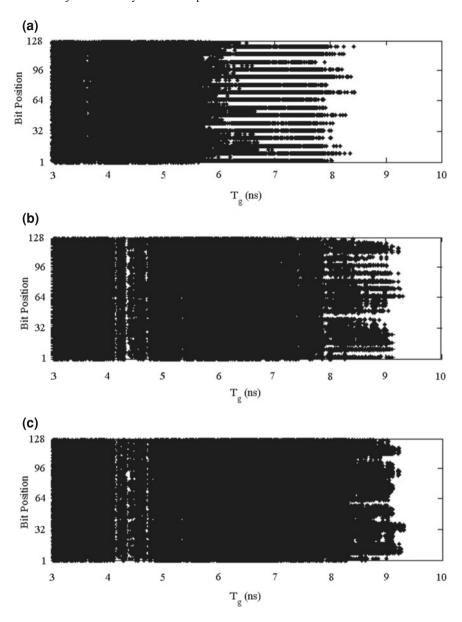

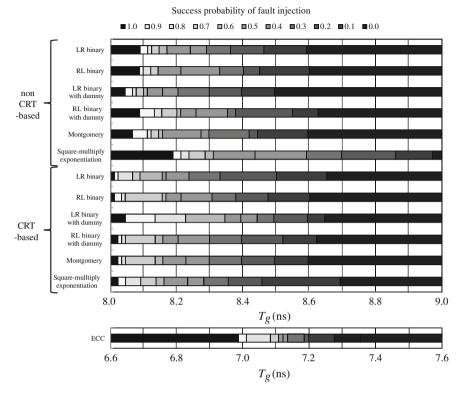

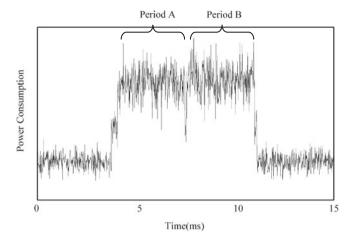

Choukri and Tunstall demonstrated in [89] that reducing the number of rounds of a block cipher is indeed possible. They used glitches on the power supply as the fault injection media, and conducted the attack on a Silvercard (PIC16F877) which does not contain any senors to protect against this sort of attack. The AES algorithm implementation used does not contain any countermeasure intended to prevent any sort of attack. The aim was to show that precise faults can be induced within a chip that can lead to the desired effect.